前言

经过一年多的学习,我发现FPGA的开发生态,可谓是十分简陋。尤其是对比软件的开发生态,可以一个天上一个地下。在我看来,这主要是与硬件的高度封闭的生态相关,这也与FPGA的市场相符,寡头垄断。而一个封闭的生态就会导致其发展十分缓慢,并且需要一直重复造轮子,这对于软件来说简直难以想象。对于软件来说,即便不懂编译原理、计算机原理等内容,也可以简简单单下载一个IDE直接进行开发。而在FPGA里,虽然也是可以下载Vivado等工具进行开发,但是他们通常缺乏IDE强大的代码分析和格式化工具。这就导致有不少人居然是用记事本或者Notepad++进行开发,这简直是难以想象。先不说Notepad++掺杂了许多政治意识形态的东西,使用Notepad++进行开发实际上也没比记事本好到哪去。

因此为了打破这个过于封闭的生态,促进开源事业的发展,我打算写几篇博文给大家一个参考,一起享受现代信息科技的先进。但可能时间不太允许我完成这份想法,只能说尽量去完成吧。

原理及其哲学

我始终认为授人以鱼不如授人以渔,不论是工具还是知识,简单的只会用是远远不够的,必须知道其背后的原理,这样才能举一反三,独立解决问题。这个过程便是理论指导实践,实践检验真理。现代人不喜欢的哲学,恰恰是现在社会的基础。如不喜欢,可跳过本章节。

对于不同的技术,我们通常会有不同的工具链,其工具链的组成也必然是不同的。但是虽然组成不同,但是多多少少会有其共通之处,这主要是因为很多技术并不是突然出现的,其必然是由前面无数技术的积累,自然而然,水到渠成的。这就意味着很多技术的工具链都会利用其依赖技术的工具链搭建而成。这便是事物的独立性与联系性,我们必须联系的看待问题。

编程语言蕴含的哲学

编程语言便是其中代表。我认为现代编程语言主要有四大主要矛盾:设计哲学、编译工具、工程管理、内存管理。这四大主要矛盾相辅相成、相互影响,最终形成一门现代编程语言。

设计哲学是现代编程语言最隐蔽但最根本的核心。任何一个语言都是围绕着一个设计哲学来设计的,比如说Python的简单易用、Rust的内存安全、Java的自动内存管理与面向对象、C++的高性能与面向对象、Scala的函数式编程与面向对象等。一门编程语言如果没有设计哲学,那必然是没有灵魂的,使用这门语言如同控制行尸走肉,事倍功半。

使用编译工具来描述主要矛盾其实不太合理,在编程语言中,有一种更为贴切的表述:动态或静态类型语言。其主要的区分为:语言中变量的类型是否是在编译过程中就确定下来的。这在大多时候表现为是否需要编译工具进行编译,但实际上也有一些动态语言可以进行编译,然后确定变量类型。因此一个矛盾通常是由许多方面构成的,不能简单的单一化或双极化看待。

工程管理大概是现代编程语言最没有争议的一个主要矛盾,比如拥有方便的包管理器、丰富的编译设置、良好的版本控制等等。但不是所有的编程语言都能达到这些要求,尤其是一些比较古老的语言如C/C++。虽然随着时代的变迁和生态的完善,他们也逐渐拥有了第三方的工程管理工具。

内存管理的方式可以说是现代编程语言最明显的特征。如果没有内存管理方式的差别,那么世界将减少一半的争端(开个玩笑)。内存管理的主要方面即:内存管理的自动化与否。手动内存管理有:C/C++、Rust等;自动内存管理有:Java、C#、Python等。

这便是我个人一些浅薄的认识,这与我们搭建的工具链并无任何关系,下面才是与之相关的关键概念。

Language Server Protocol

The Language Server protocol is used between a tool (the client) and a language smartness provider (the server) to integrate features like auto complete, go to definition, find all references and alike into the tool. ——official Language Server Protocol specification

根据官方的定义,LSP是一种通信协议,用于连接客户端与Language Server(编程语言分析工具),以便提供相应语言的补全、提示、查找等功能。这个LSP的发明是跨时代的,因为以往的IDE通常是自己发明的一套语言分析工具,只对一种语言有效,即仅对一种语言提供代码补全、语法提示等功能。同时由于不是所有IDE都有实力自己开发语言分析工具,并且每个IDE有着不同的API,因此编程语言的开发者需要为N个IDE开发相应的语言分析工具。这实在是过于浪费时间和金钱,因此微软就提出了这个概念及系统,并率先在VSCode上使用。

此后,许多语言的开发者只需开发一次Language Server便可实现多个IDE的适配。甚至,假如有人认为官方的Language Server过于简陋,性能过于差劲,他完全可以自行开发一套Language Server。因此,后来也涌现了不少的Language Server,更有甚者被官方招安。详情可以查看Langserver.org,里面列出了许多语言的Language Server。

因此,虽然VSCode被许多开发者赞誉,但其本身的使用难度可不容易。只有前端开发者能够即开即用,因为VSCode仅自带了Web的Language Server。看到这,大概就会明白,为什么有那么多初学者吐槽VSCode没有代码补全、语法提示了。因为虽然VSCode支持LSP,但是没有Language Server也是巧妇难为无米之炊。

Code Formatter

Code Formatter,即代码格式化工具。顾名思义,就是用来给代码进行格式化操作的。这主要是由于程序员的水平参差不齐,许多人没有良好的代码风格,经常是这边多个空格,那边少个回车。虽然代码都能正常运行,但是对于后面接手的人可就不好受了,十分辣眼睛,影响效率。一个好的代码风格甚至可以提高代码的阅读效率。 同时,由于社会的高度分工化,加上每个人的代码风格又不一样,对于大型合作项目来说管理就很不方便。

因此为了解决这两个问题,代码格式化工具就出现了。在解决了这两个问题的基础上,同时也方便程序员编写代码,只要设置完格式化工具,即可随心编写代码,而不用关注代码风格的问题。

Windows下FPGA开发工具链安装指南

由于本工具链是基于VSCode的,因此首先确保已经安装完成VSCode。VSCode官网直达。

安装 Language Server 与 Code Formatter

这里我综合考虑了更新频率和功能性选择了以下的 Language Server 与 Code Formatter,如果你想使用其他的也是可以的。只是下面的安装指南会以我的Language Server 与 Code Formatter为例。

- SVLS:全称为SystemVerilog language server,顾名思义即SystemVerilog的Language Server

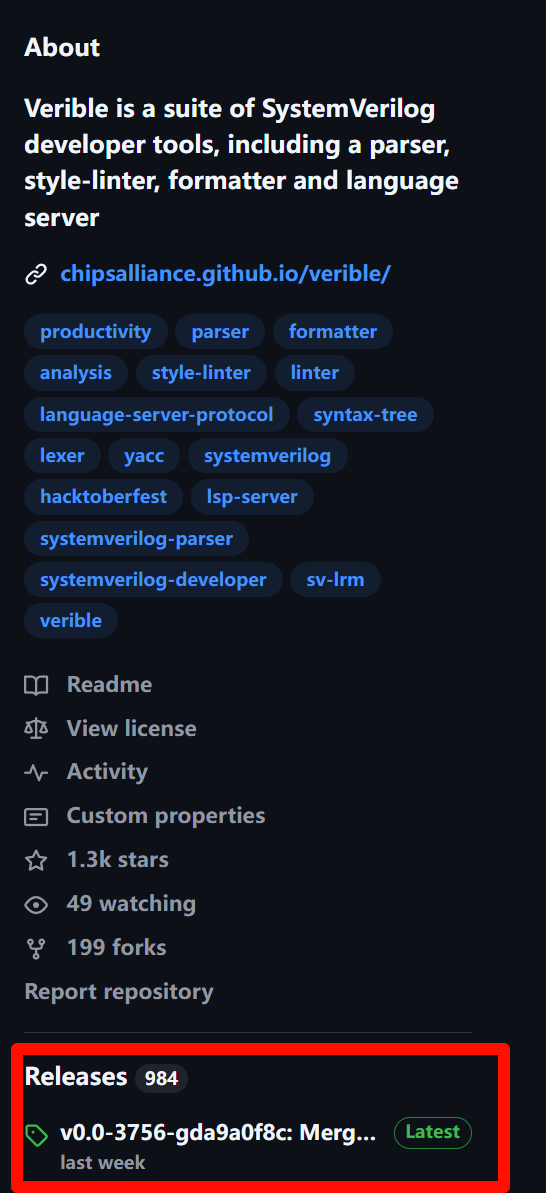

- Verible:一套SystemVerilog / Verilog的工具链,包括基本的Language Server、formatter、style-linter。

- VSG:VHDL的风格化检查的工具。

- GHDL:一套VHDL的工具链,包括编译、仿真、综合、语法检查等功能。

下载安装指南

一般安装方式就是跟随Github的安装说明即可,但有一些工具安装需要手动安装。比如VSG就可以直接用Python的PIP安装,Python相关安装请参考下面的内容。这里就不得不感慨,VHDL的生态果然比Verilog好太多了。同时Linux的FPGA开发环境比Windows要方便的多。

进入Github仓库的发布页,找到最新版。

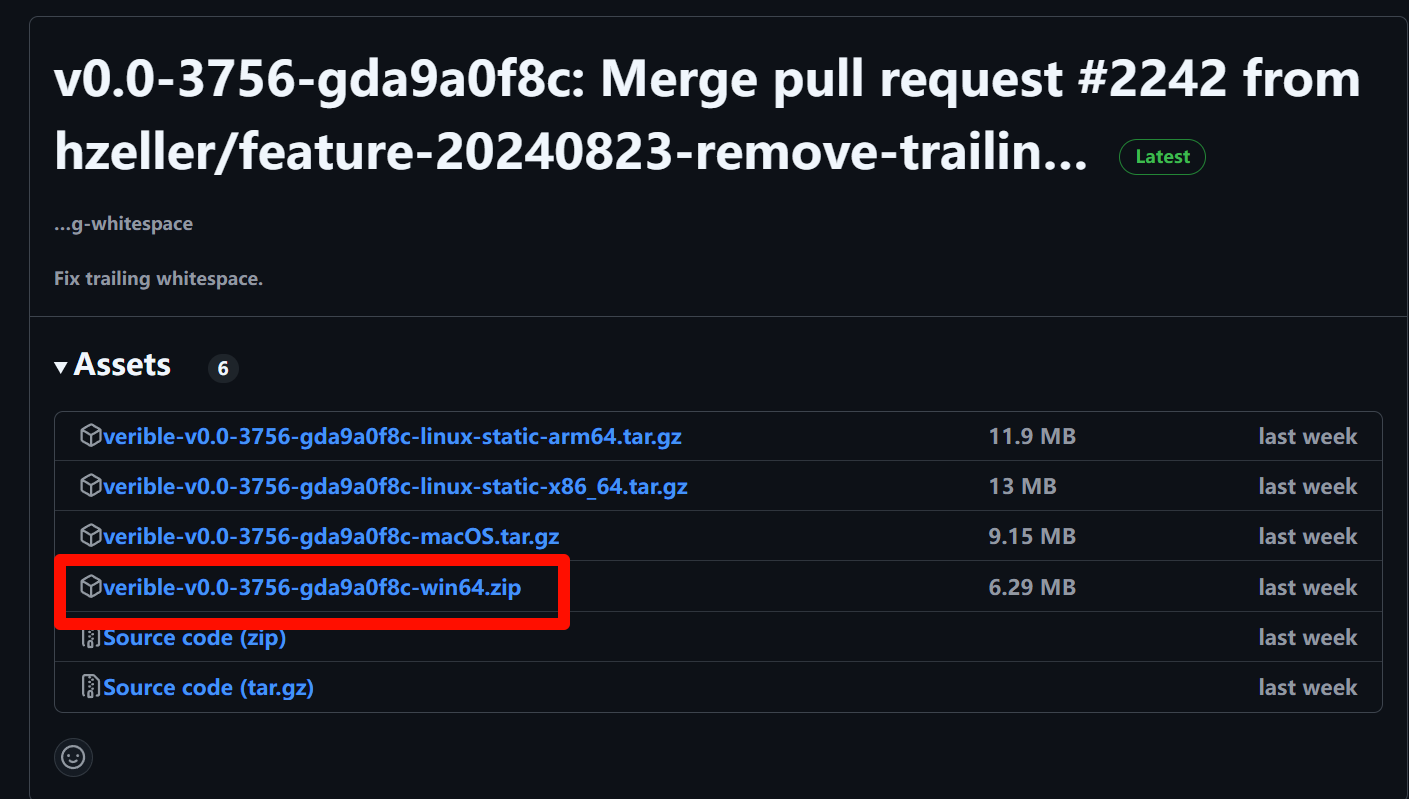

选择相应的系统和指令集(AMD与Intel选64,高通选arm)。

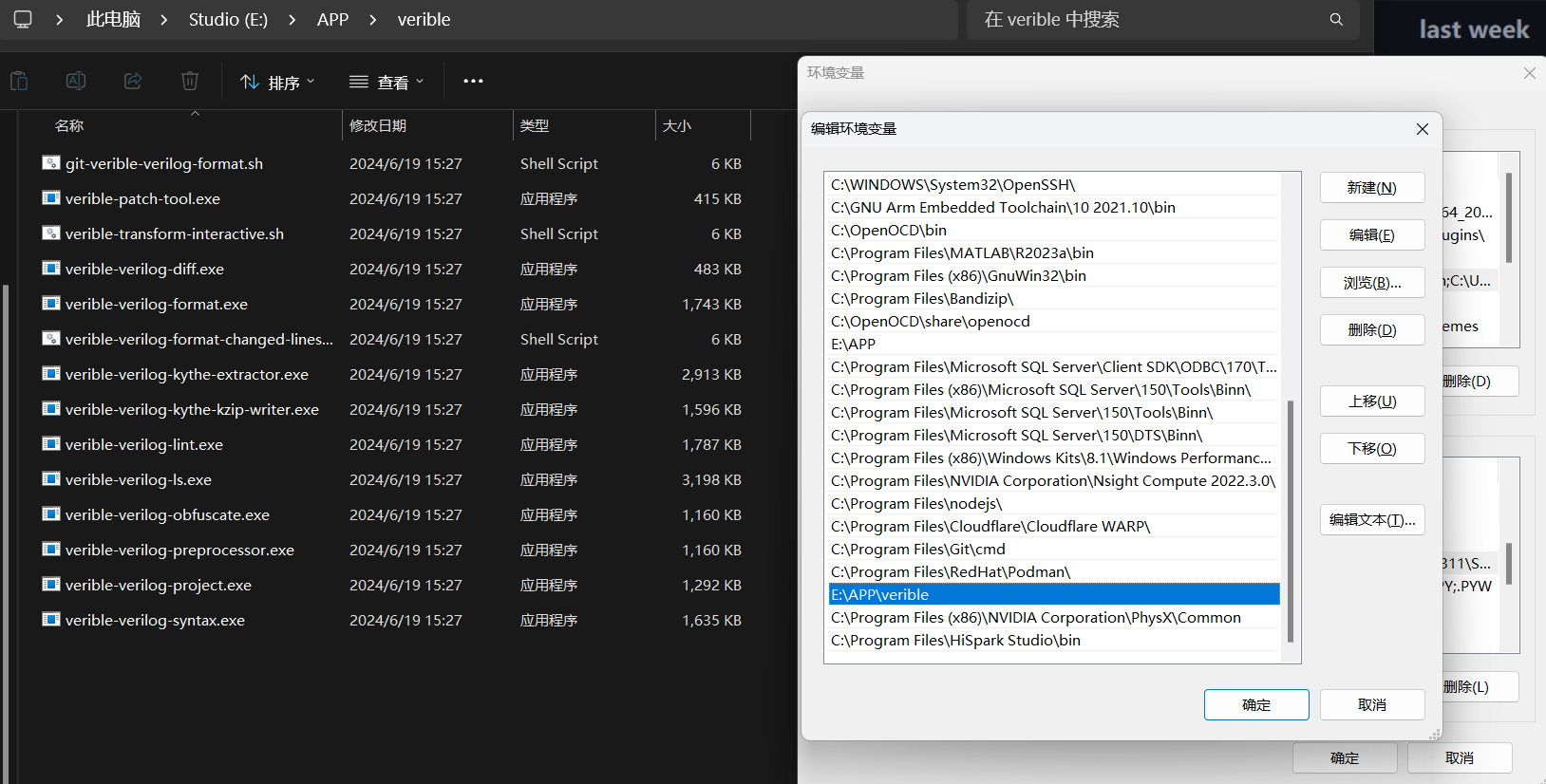

下载完成后,解压到一个特定的地方,然后添加该目录地址为PATH系统变量(确保该目录下存在相应的二进制可执行程序)。

方法一:简单的支持

如果你只是想用VSCode写代码,然后使用其他工具进行工程管理,那么使用一个简单的扩展即可。这种方式面对的场景较多,毕竟大部分公式的FPGA的开发环境并没有那么先进,大部分都是使用比较落后的管理方式。

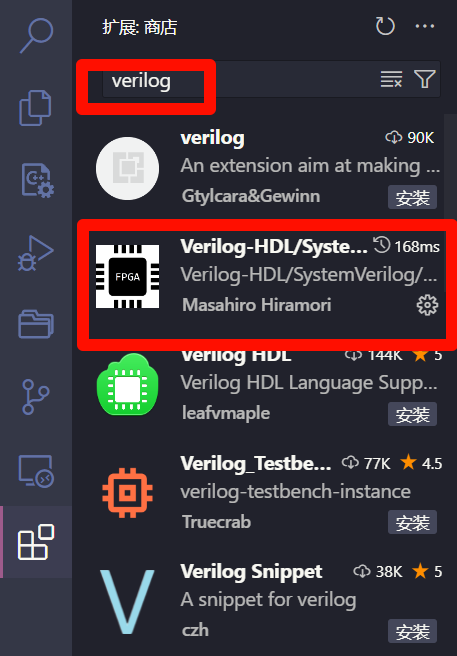

搜索扩展Verilog,找到相应扩展并安装。该扩展主要是实现了Verilog、SystemVerilog等硬件描述语言的LSP和语法检查(但不建议使用该扩展进行语法检查,对Windows支持极差),并为多个Language Server和Code Formatter 提供支持。更多功能以及具体支持情况请看该扩展的介绍。

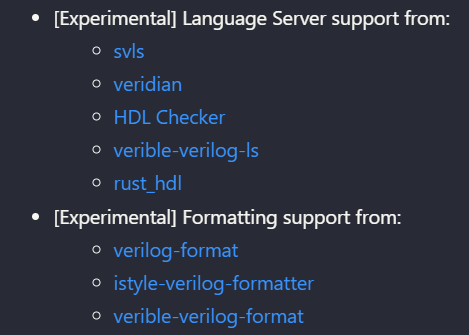

具体支持的Language Server和Code Formatter如下:

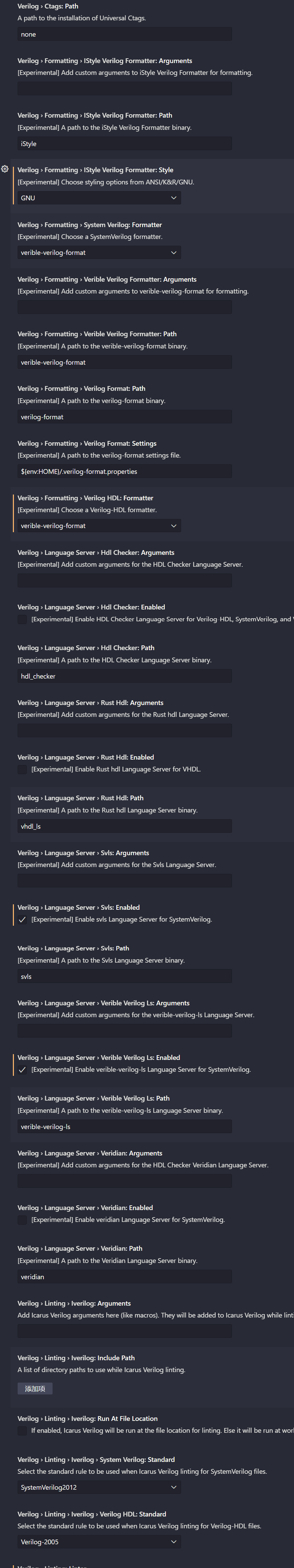

修改Verilog扩展设置即可,黄色处即为需要修改的选项,这里我仅设置了 SystemVerilog / Verilog 的相关内容,VHDL请参考图片进行设置。

方法二:高级支持

对于更高级的支持可以使用TerosHDL。这是一个ASIC/FPGA开发工具套件,包含了一些基本的工具链、工程管理、生成原理图等工具,非常容易配置和使用。

Python的相关安装

Python可以参考官方的安装说明,已经非常详细了。这里仅提供一些安装建议:

- 如果没使用过Python且后续不考虑学习Python,可以考虑安装MiniConda即可。

- 如果没事用过Python且后续考虑学习Python,那安装Anaconda。

- 如果有使用Linux并且比较熟悉Python,通过Pyenv安装即可。

- 选择Python的版本不要太新,也不要太久,一般低一个大版本即可。

安装TerosHDL与Cocotb

Cocotb是一套基于Python的开源测试和验证框架,这套工具是可选的,不安装也不会影响TerosHDL的运行。

打开命令行,输入pip install teroshdl与pip install cocotb即可完成安装。安装完后可以输入pip list查看所有Python库,查看是否有teroshdl与cocotb。

然后安装Make,由于官网只有源码,这里给出第三方编译的Windows版本,下载相应系统与指令集的最新版本并安装即可,同时记得添加环境变量。Make是一套C/C++的编译工具,用于解析编译脚本并执行相应的编译操作。

或者也可以参考官网的安装说明,先安装Chocolatey或Scoop,通过这两个包管理器直接安装Make。我个人更喜欢Scoop,因为他包更多,并且开源易于添加包;Chocolatey主要是官方维护,包的质量很高,但有些付费。

- Chocolatey:

choco install make - Scoop:

scoop install make

安装完Make后,执行make --version,确认Make是否正确安装。

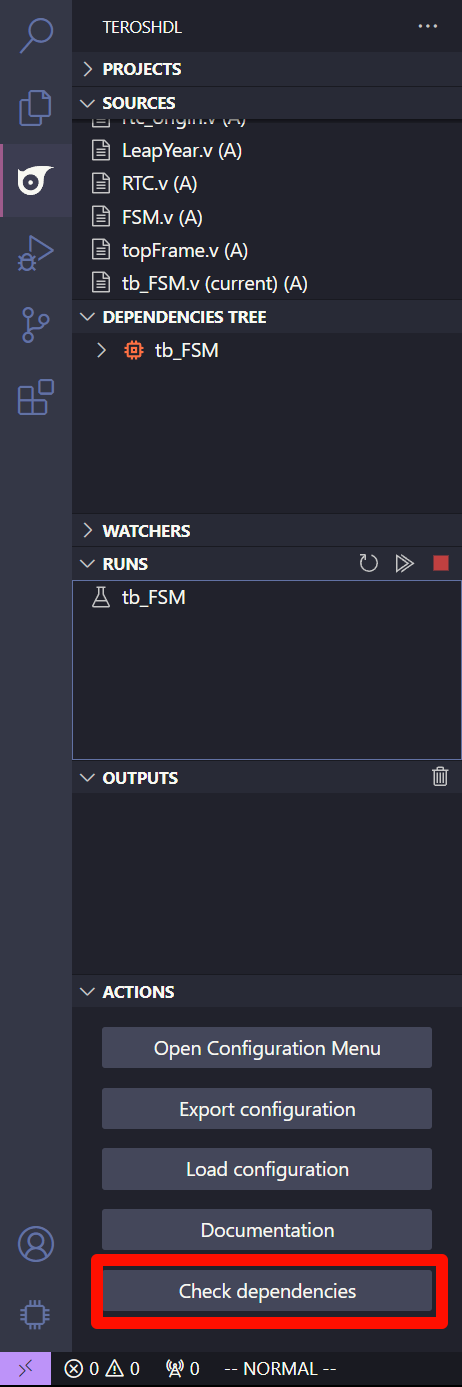

最后在VSCode中安装TerosHDL即可。安装完后,打开插件,检查依赖是否能够正常识别。

配置TerosHDL

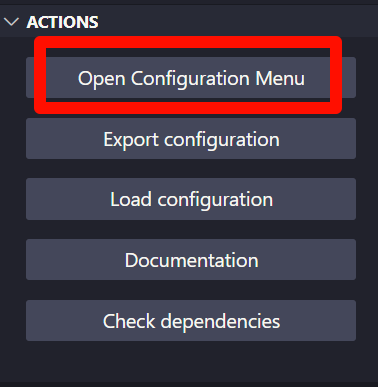

打开TerosHDL设置选项。

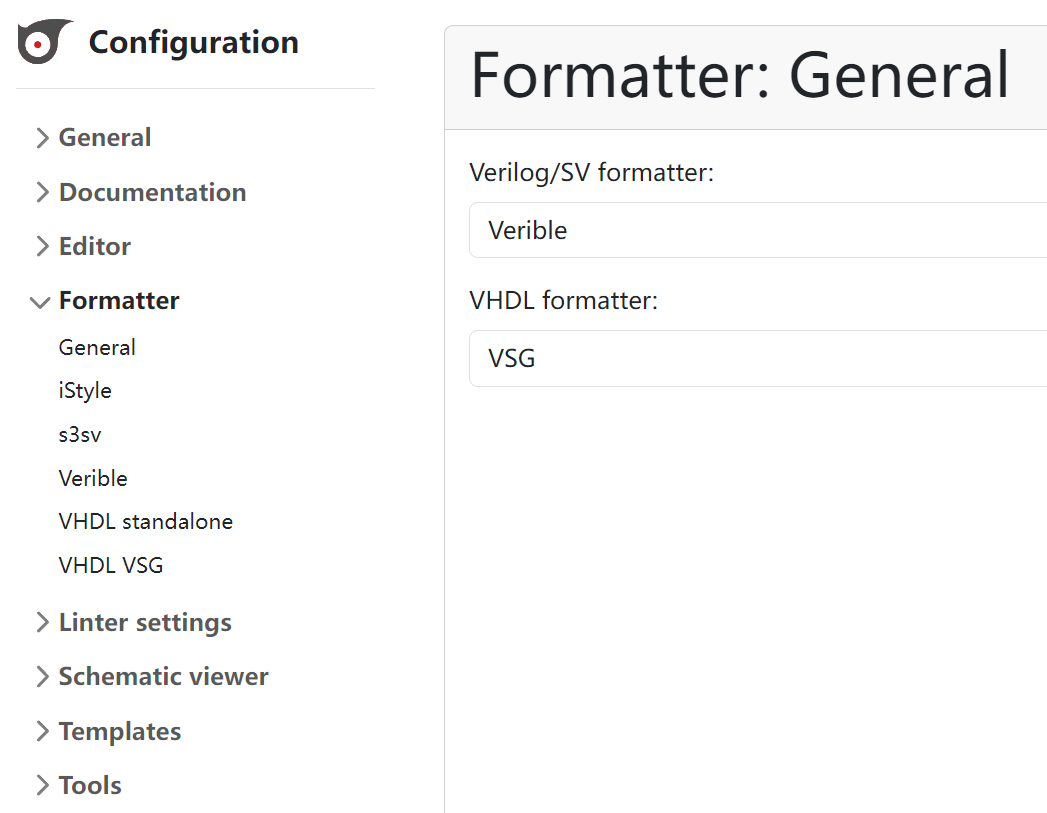

设置Code Formatter。

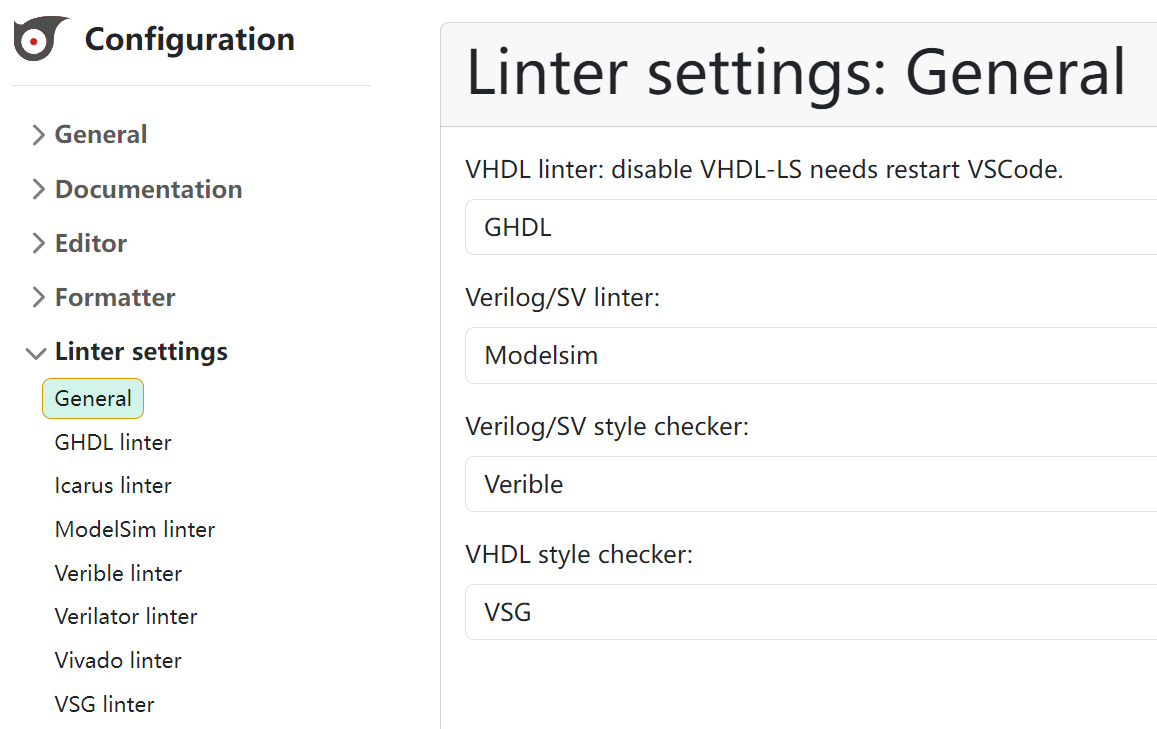

设置语法检查,注意ModelSim需要安装在默认位置,否则无法识别需要重新配置路径。

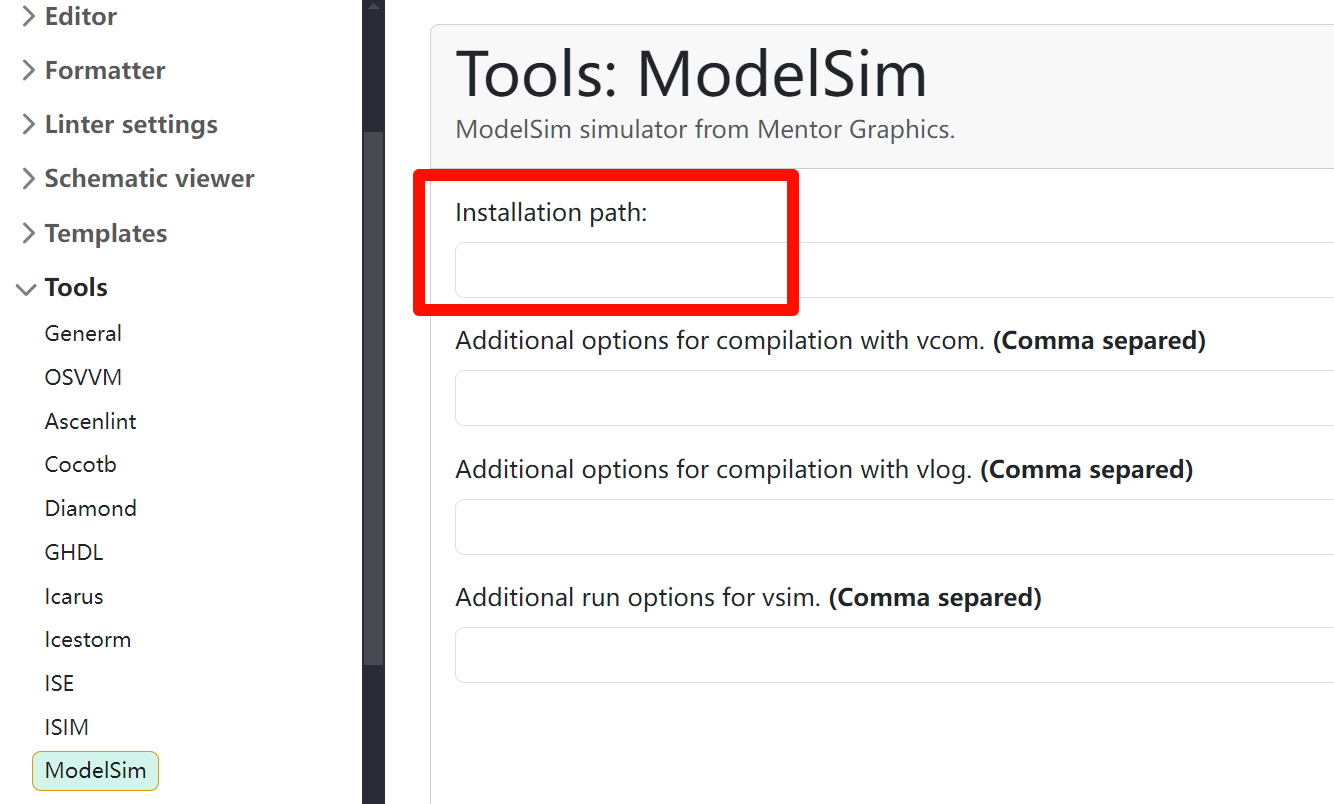

配置安装路径,其他工具也是同理,如果不配置系统环境变量,则需在下面菜单中配置安装路径。

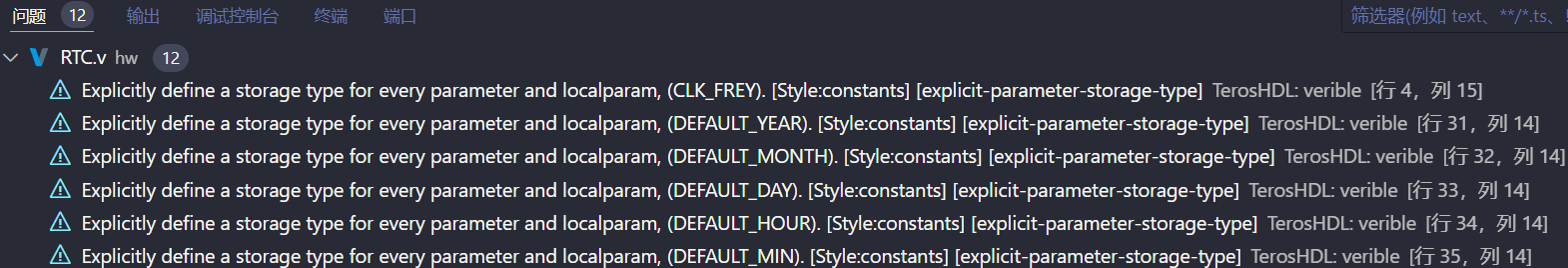

保存并重启后,你应该就能享受到美妙的写代码体验了。默认会在下面输出报错和警告,并在文本编辑区域内提示。

Linux下的FPGA开发工具链安装指南

你都用Linux了你还问我?看官网教程就完了,我绝不会说是因为我太懒了。